Китайский программатор ПЛИС Xilinx

- Цена: $24.82

- Перейти в магазин

Когда в прошлом обзоре писал про ПЛИС, понял, что мало кто с ними сталкивался, у всех возникает куча вопросов чем ПЛИС лучше ардуины и т.д. Ну и раз во всех новичковых обзорах ардуин моргают лампочкой, то в этом обзоре хотел бы рассказать про то, как и с помощью чего залить прошивку и показать как создать тестовую прошивку, дёргающую ногу со светодиодом.

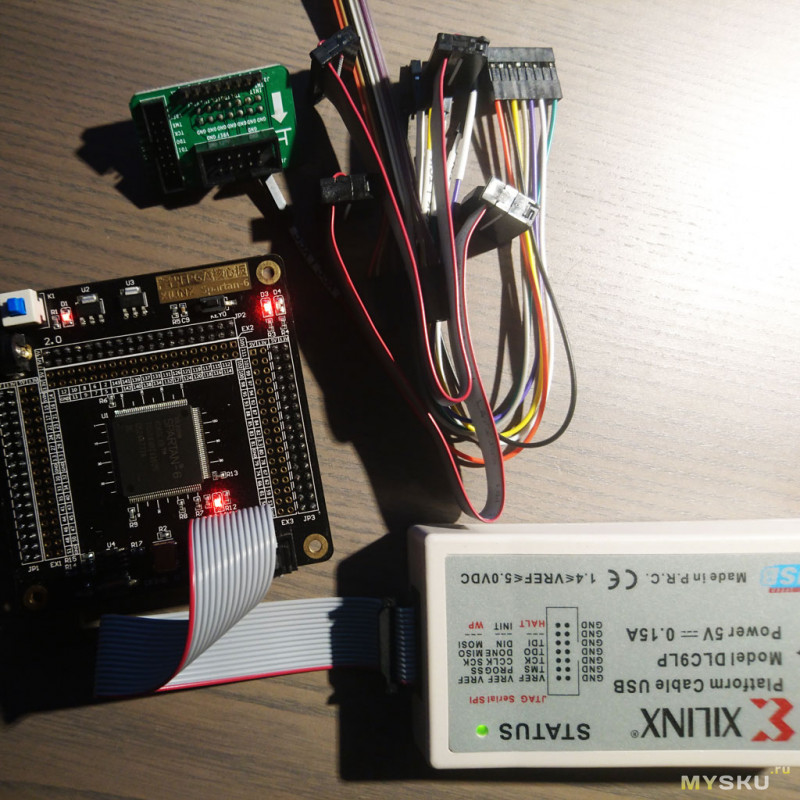

Недавно мне приехала вторая отладка, но уже с более продвинутым кристаллом Xilinx Spartan 6 xc6slx9 (по сравнению с Spartan 3 из прошлого обзора). Для начала хотелось проверить её работоспособность, в простейшем случае моргнуть светодиодом.

Вообще большинство ПЛИС Xilinx хранят конфигурацию (прошивку) в энергозависимой памяти, которая туда попадает или из SPI-флешки подцепленной к определённым ножкам, либо программированием напрямую программатором через интерфейс JTAG (spi-флешку можно тоже записать по JTAG-у).

Вот тут-то и понадобится специальный программатор. Можно приобрести тут оригинальный Xilinx DLC10 за 23791 р. и китайский DLC9LP на Ali как обозреваемый или тут такой же за 3167 р. Но на Али вдвое дешевле…

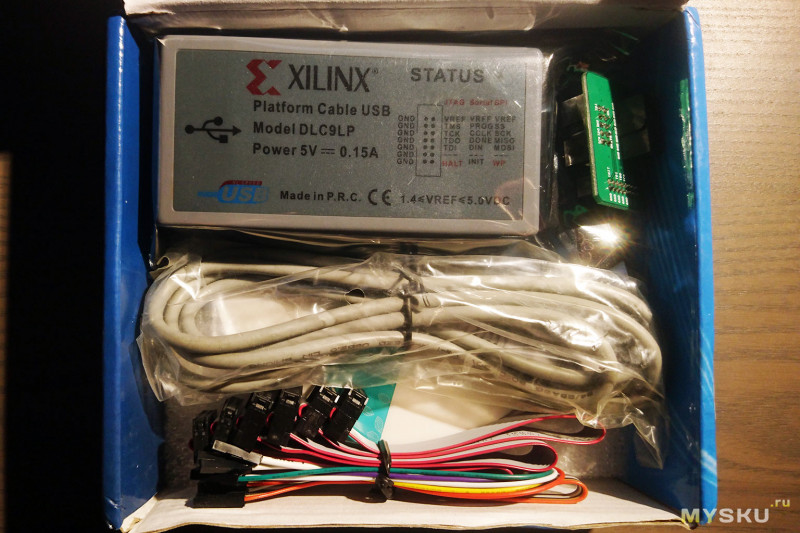

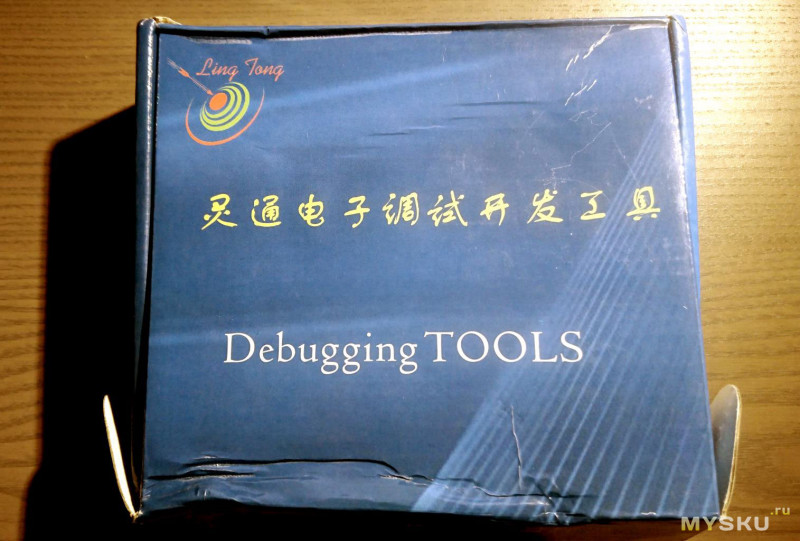

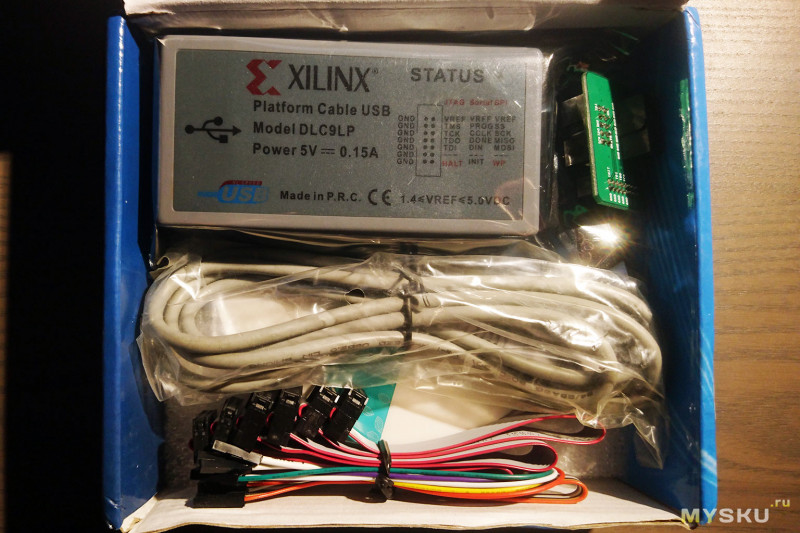

Приехал он в немного помятой коробочке, в комплекте много разных переходников и шлейфов и DVD-R диск с каким-то софтом (наверное старый Xilinx ISE какой-нибудь прислали).

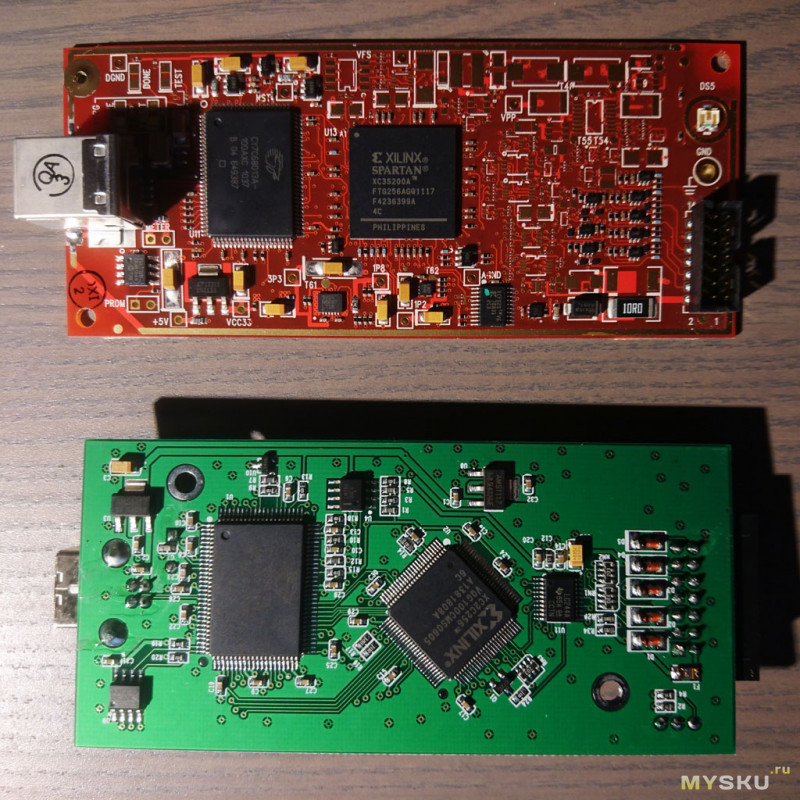

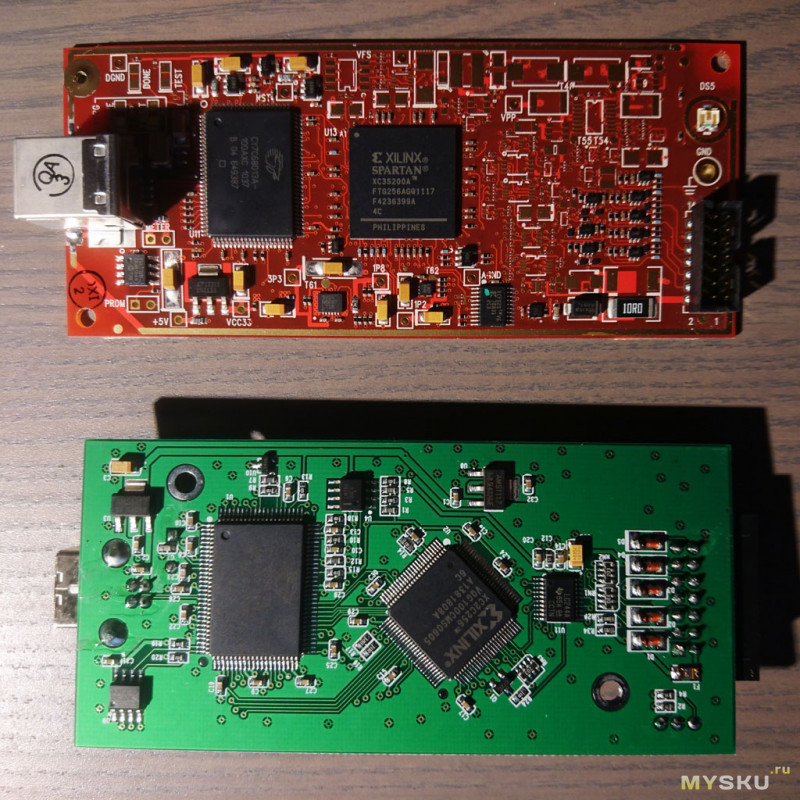

По размерам примерно соответствует оригинальному, только разъём перенесли в торец коробочки.

Собран на XC2C256 CoolRunner-II CPLD, в отличие от оригинального на Spartan 3 xc3s200a, отсутствует металлический экран, как у фирменного. Снизу на платах ничего нет, только дорожки и контактные площадки. (Больше не расскажу, как работает я не в курсе).

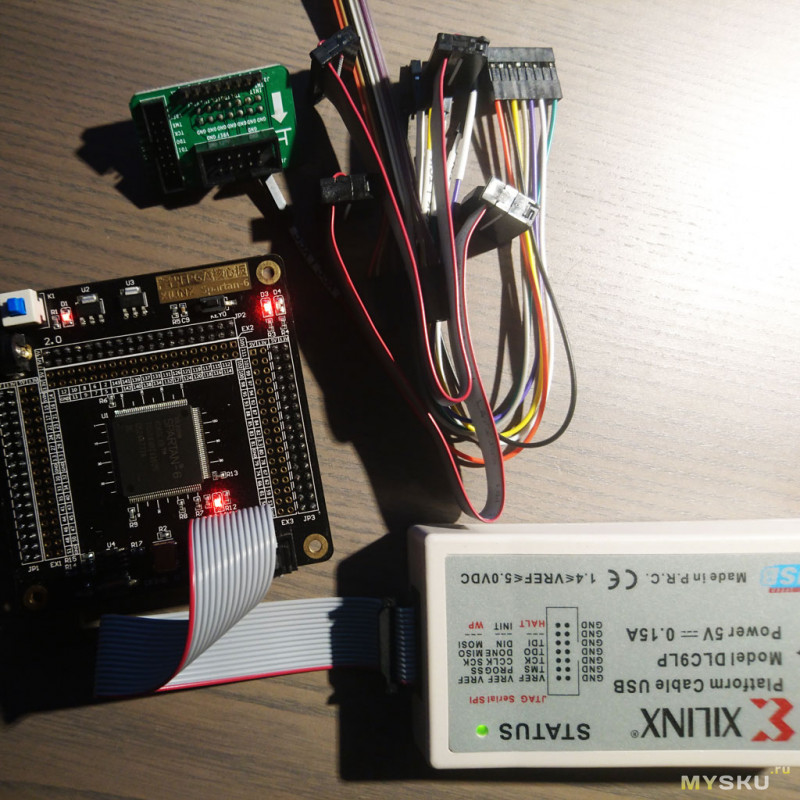

Далее подключаем usb к ПК, шлейф к ПЛИСине, когда установится драйвер загорится оранжевый светодиод, при подаче питания на ПЛИС загорается зелёный.

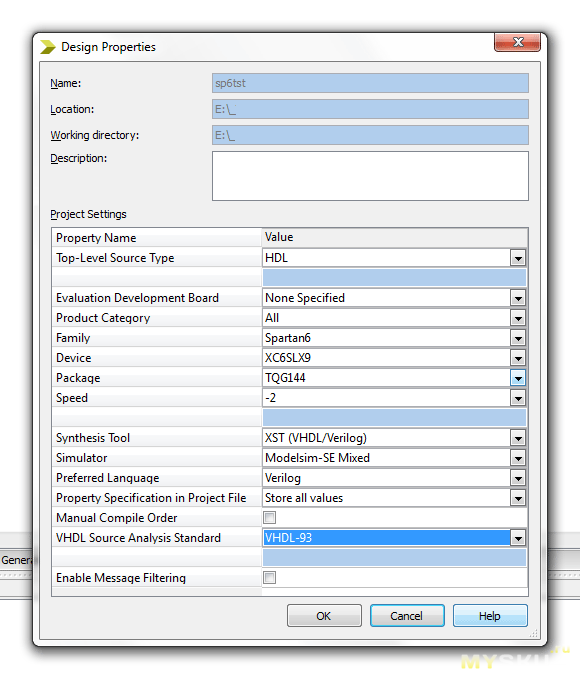

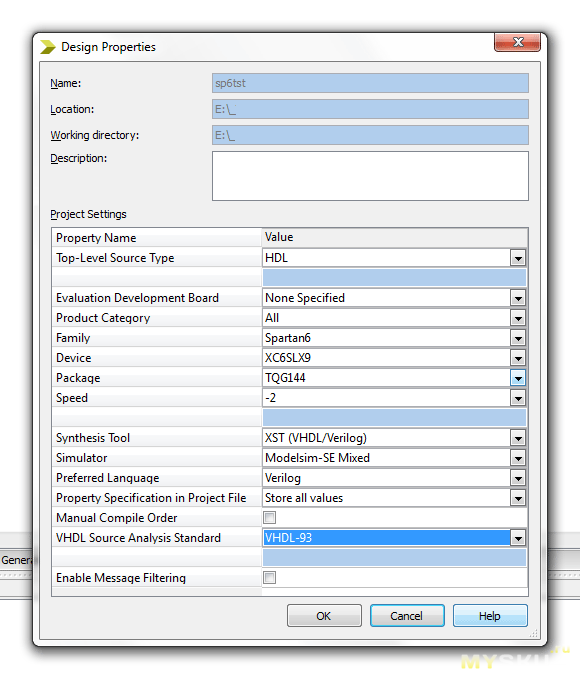

Теперь создаём в Xilinx ISE новый проект с настройками под нужную ПЛИС, например:

Добавим в него Verilog модуль следующего содержания:

Входом модуля является только тактовый сигнал clk с генератора 50 МГц, внутри объявлен регистр счётчика на 23 бита, который инкрементируется на 1 с каждым положительным фронтом тактового сигнала. Выход модуля — однобитный регистр ld, значение которого совпадает с последним битом счётчика (правда задержанное на один такт = 20нс).

Ну и ещё нужно указать синтезатору на каких ножках стоит генератор такта и светодиод, добавим файл Implementation constraints file:

Всё, теперь выбираем «Top module» наш файл main.v и жмём Generate programming file.

Теперь можно загрузить конфигурацию через приложение ISE iMPACT.

Светодиод мигает, программатор и отладочная плата работают.

Недавно мне приехала вторая отладка, но уже с более продвинутым кристаллом Xilinx Spartan 6 xc6slx9 (по сравнению с Spartan 3 из прошлого обзора). Для начала хотелось проверить её работоспособность, в простейшем случае моргнуть светодиодом.

Вообще большинство ПЛИС Xilinx хранят конфигурацию (прошивку) в энергозависимой памяти, которая туда попадает или из SPI-флешки подцепленной к определённым ножкам, либо программированием напрямую программатором через интерфейс JTAG (spi-флешку можно тоже записать по JTAG-у).

Вот тут-то и понадобится специальный программатор. Можно приобрести тут оригинальный Xilinx DLC10 за 23791 р. и китайский DLC9LP на Ali как обозреваемый или тут такой же за 3167 р. Но на Али вдвое дешевле…

Приехал он в немного помятой коробочке, в комплекте много разных переходников и шлейфов и DVD-R диск с каким-то софтом (наверное старый Xilinx ISE какой-нибудь прислали).

По размерам примерно соответствует оригинальному, только разъём перенесли в торец коробочки.

Собран на XC2C256 CoolRunner-II CPLD, в отличие от оригинального на Spartan 3 xc3s200a, отсутствует металлический экран, как у фирменного. Снизу на платах ничего нет, только дорожки и контактные площадки. (Больше не расскажу, как работает я не в курсе).

Далее подключаем usb к ПК, шлейф к ПЛИСине, когда установится драйвер загорится оранжевый светодиод, при подаче питания на ПЛИС загорается зелёный.

Теперь создаём в Xilinx ISE новый проект с настройками под нужную ПЛИС, например:

Добавим в него Verilog модуль следующего содержания:

module main( input clk,

output reg ld

);

reg [22:0] cntr;

always@(posedge clk) begin

cntr <= cntr+1;

ld <= cntr[22] ;

end

endmodule

Входом модуля является только тактовый сигнал clk с генератора 50 МГц, внутри объявлен регистр счётчика на 23 бита, который инкрементируется на 1 с каждым положительным фронтом тактового сигнала. Выход модуля — однобитный регистр ld, значение которого совпадает с последним битом счётчика (правда задержанное на один такт = 20нс).

Ну и ещё нужно указать синтезатору на каких ножках стоит генератор такта и светодиод, добавим файл Implementation constraints file:

NET "clk" LOC = "P55";

NET "ld" LOC = "P92";

Всё, теперь выбираем «Top module» наш файл main.v и жмём Generate programming file.

Теперь можно загрузить конфигурацию через приложение ISE iMPACT.

Светодиод мигает, программатор и отладочная плата работают.

Самые обсуждаемые обзоры

| +93 |

5628

180

|

| +89 |

2157

32

|

| +73 |

2531

37

|

| +241 |

4838

40

|

Я прочитал, и заказал еще утром.

Автору — спасибо за вариант.

очевидно, что это не стоимость разработки

Я не увидел в обзоре, что ПЛИС лучше ардуины. А если мне будут нужны мегагерцы и внешняя логика в одном чипе, по такой цене разработки возьму малину или апельсин (которые дешевеют в отличии от сабжа). Потому, что так удобнее. Потому, что это доступно уже и детсаду и в итоге даст бОльшее кол-во полезного продукта на выходе.

Хотя дальше до ката я расписал, что в статье будет только стандартный Hello world! с морганием.

Что одна мигалка не будет лучше другой думаю все сразу поняли.

Это все равно что сравнивать паровоз и велосипед потому что у них есть колеса.

Вашим малинам с апельсинами нужна операцонная система и приложения. ПЛИС работают сами по себе.

полагаю, именно по этой причине, столетие назад люди пересели с лошадей на автомобили (еще и перспективный ресурс).

И, _сами_по_себе_, работают только вечные двигатели. Все остальное нужно прошивать, заряжать, кормить, итд итп…

Система Оберон, реализованная на доступной FPGA-плате

У FPGA задачи обычно аппаратные, взаимодействие с железом и быстрая обработка сигналов, тогда как у контроллера обычно управляющая функция. Контроллер ограничен в своей работе последовательным исполнением команд и некоторым жестко заданным списком встроенной периферии. Вы не можете контроллером (хоть ардуиной, хоть малиной) одновременно обрабатывать нажатия кнопок, принимать данные по SPI и выводить данные на экран. А на FPGA можете.

FPGA чаще всего дополняет микроконтроллер как набор необходимой внешней периферии различного уровня сложности. От простого SPI-трансивера на десяток каналов до графического контроллера с нужной системой команд и ускорителем графики. Да даже ядро той же меги можно запихнуть в FPGA и приделать всю нужную периферию, которая оригинальной ардуине и не снилась :)

Приведу пример из моей практики — нужно было сделать цифровой фильтр на два канала (одновременно). Данные с АЦП поступают с частотой 40 кГц, фильтр состоит из трех ступеней, общее количество коэффициентов во всех трех ступенях — около двух с половиной тысяч. На всякий случай поясню по цифровому фильтру: при каждом новом значении от АЦП производится умножение на каждый из коэффициентов, после чего все произведения суммируются и делятся на число коэффициентов. И вот 40 тысяч раз в секунду нужно было произвести около 400 умножений в первой ступени фильтра, просуммировать все это, поделить, передать результат второй ступени, произвести там около 800 умножений, суммировать, поделить, передать результат третьей ступени, произвести в нем около 1300 умножений, просуммировать, поделить. И все то же самое проделывать синхронно и на втором канале. Плюс разные дополнительные функции — управление АЦП, общение с микроконтроллером, слежение за несколькими датчиками, несколько каналов SPI и I2C для микроконтроллера. Со всем этим справилась одна сравнительно недорогая FPGA, работавшая на частоте 110 МГц. Малины с апельсинами могут о таком только мечтать, хоть у них и на порядок больше мегагерц, чем у FPGA :)

Делал на одном из младших SHARC-ов — красота…

Вот, если интересно, скриншот таблички с описанием организованных в FPGA регистров — joxi.ru/1A5xOejInJZzJ2

А на Шарке у нас был другой проект, но как программист DSP уволился, так Шарки и перестали использовать — никто больше не хотел изучать их, да и дорогущий отладчик для них умудрились спалить, на новый деньги выбивали бы пол-года :)

Просто прочитал:

К сожалению, весьма знакомая ситуация.

Изначально я вообще чистый электронщик — 0701, если кто помнит :)

По ней и работал в НИИ, занимался именно разработкой, несколько моих плат летали, может, и сейчас летают.

Так сложилось, что надо было кому то заняться MCS'51 семейством, ну, я и занялся.

В одном проекте я писал один кусок — распознавание кода Морзе с ключа (не с клавиатурного датчика типа Р010 — именно с ключа, со всеми свойственными человеку колебаниями всех параметров), другой, который программист по профессии — писал генерацию кода.

Наверное, все хорошие программисты были заняты нормальной работой, по профилю (это была немного левая работа), поэтому и генерацию пришлось писать мне.

Потом мне же пришлось писать и оболочку — ею изначально занимался другой программист.

Потом мы начали делать приборы для железной дороги — в том числе и на 51-м.

Потом перешли на более сложные сигналы, где 51-й явно не плясал — вот тогда шарк и применили.

В паре с молодым, но профессиональным (в смысле записи в дипломе и трудовой) программистом.

Когда опять ничего не получилось — свалили опять на меня (наверное, потому что я редко от чего отказывался и практически всегда делал то, за что брался).

Благо, к тому моменту появился у нас товарищ — он моделировал в маткаде фильтры, а я уже воплощал в железе.

А после того, как поговорил буквально с полчасика с программистом командированным (по другому вопросу командированным), но который действительно программировал под шарки) — так и вообще проблем с ресурсами не стало, просто пара маленьких хитростей, немного увеличивающих код, но резко сокращающий его размера в теле цикла.

То есть у вас то же самое — просто надо было кому то взяться, другой вопрос — я тогда думал, да и сейчас придерживаюсь того же мнения, что программы под контроллеры должен писать по большому счету тот, кто понимает их структуру, то бишь железячник.

Примерно так же я для альтеры стал писать — когда от меня просили нарисовать схему железа, которое реализовывала запрограммированная мной ПЛИС, я это не всегда мог сделать :)

И это в основном потому, что была у нас сильная команда, как то хорошо получалось вместе работать, не делили работу на свою и чужую.

… от блин написал то всякого… :)

Чистый программист был только один — который писал «верхний» софт — драйвера и управляющие программы для компьютеров.

В чем самый кайф и был :)

А вот подробности сейчас уже не помню — там надо было именно в железо смотреть.

Проверка точно ни с чем не совмещалась, точнее — совмещалась, но только результат проверки был готов только к следующему такту.

Хитро там все было.

Но интересно… :)

семерых одним ударомсразу несколько умножений/сложений.И вот в андроиде «рюшечек» больше чем в винде, а он на юниксе.

Поэтому, обычно, ПЛИС и контроллер работают в паре: первая выступает в роли байто-молотилки, а второй в роли управляющего органа. Попробуй сделать генератор FullHD (точнее 1920x1200 UXGA) на AVR или ARM, что бы ещё ресурсов для остальной логики осталось.

Ещё, часто на FPGA (сиречь — ПЛИС) прототипируют специализированные чипы, отлаживают, после чего заказывают в железе и получается… ASIC! Который на производстве дешевле и, чаще, быстрее. Помните эволюцию расчёта биткойнов: CPU -> GPU -> FPGA -> ASIC. Одно и тоже, в функциональном плане, устройство на ASIC и FPGA будет ощутимо различаться в цене в пользу первого. Но вторым можно обновить прошивку :)

Резюмируя, FPGA — это набор вентилей и вспомогательных устройств и которых синтезируется специализированная схема. Например — процессор: geektimes.ru/post/257370/ :) Или сэмулировать другую какую микросхему в вашей плате.

ЗЫ А мигалку вообще можно сделать на двух транзисторах или NE555 (при схожей цене — мороки меньше).

ЗЗЫ habrahabr.ru/post/234369/, на 10G Ethernet вы бы попросту отдали бы весь процессор общего назначения. Поэтому на переднем крае обороны — FPGA или ASIC (если в вашу карту грузится микрокод, скорее всего — первый вариант).

«китайский программатор» точно такая же тавтология как и «масло масленое»

Есть отличия и в построении ячеек, но они не столь принципиальны.

ЗЫ Вообще, терминология у буржуев зело обширная. Даже для такого дела как туризм: хиккинг, треккинг, бекпакинг, сноушуинг (и это только пешка) и ещё тьма тьмущая. А у нас только: горный, пеший, водный, вело и т.п.

Ну, к примеру, из-за особенностей реализации ячеек простой счетчик в FPGA займет значительно меньше ячеек, чем в CPLD :) Или вопрос защиты прошивки: если многие CPLD имеют возможность защитить конфигурацию от считывания, то большинство FPGA этого никак не предусматривают, конфигурация в них заливается «открытым текстом» — подключайся и спокойно читай :)

XC9500XL построена на макроячейках, 36-288 штук, до 178 MHz или 208 MHz (288 макроячеек). Интересна наличием легкопаяемых моделей со всего 44 ножками и шагом 0.8. Также есть 64- и 100-пиновые с шагом 0.5, вполне приемлемо, как у STM8/32. Ещё есть модели в PLCC корпусах, их можно ставить в специальный кредл.

CoolRunner-II — оптимизированы для низкого потребления, сохраняя производительность и простоту использования. Рассчитаны на питание 1.8 вольт, ввод/вывод от 1.5 до 3.3 В. 180 нм технология, 32-512 макроячеек, 179-323 MHz (меньше ячеек — больше частота). Также встречаются в паяемых корпусах, как и 9500.

Из FPGA Xilinx предлагает серии Spartan-6, Artix-7, Kintex-7, Virtex-6 и 7. Virtex-7 — монстр с 2 миллионами логических блоков и до 1200 пинов.

upd: заказал на ebay 5 шт за 8$ поиграться :)

Они бывают в 44-pin VQFP, думаю, реально припаять.

переключается кнопкой на корпусе, определяется как родной.

Покупал за 1800 до повышения.

Шил спартан и циклон.

Вот, кстати, он на EEV www.eevblog.com/forum/microcontrollers/fpga-programmer/

Я так понимаю что тут много технарей.

У меня вот лежит DE0-Nano, Отладочная ПЛИС плата на базе FPGA Altera Cyclone IV.

Лежит уже больше года. Досталась новой.

Цену реальную знаю. Может найдётся желающий купить дешевле цены производителя? Пишите в лс.

Понимаю что здесь не торговая площадка. Но может кому действительно нужна, а у меня вот лежит без дела.

А если нужен только программатор, то как вариант еще такое бывает Копия Mojo V3 (полагаю). Дороже всего лишь на 10 у.е. при том же функционале. Данная плата конфигурируется по USB, не требуя отдельного программатора.

Но отладочные умения вашего устройства все-таки интересуют.

Посмотрел бы я, что бы сделали на ардуине те, кто выше писал.

Тогда, правда, ардуин не было — тогда и пики то только начали появляться…